# UFPR - DInf - Bacharelado em Ciência da Computação CI212 - Organização e Arquitetura de Computadores <2001-1>

## Primeira Prova

- 1) Escreva um programa eficiente em C para copiar um string de uma posição para outra de memória. Ignore a possibilidade de sobreposição. Traduza-o para a linguagem de montagem do MIPS. [5 pontos]

- 2) Desenhe o esquema de uma ULA de 4 bits que permite a execução das seguintes instruções (em versão de 4 bits, é óbvio): [10 pontos] sll, slr (shift logical {left,right} de uma posição) slt (set on less than)

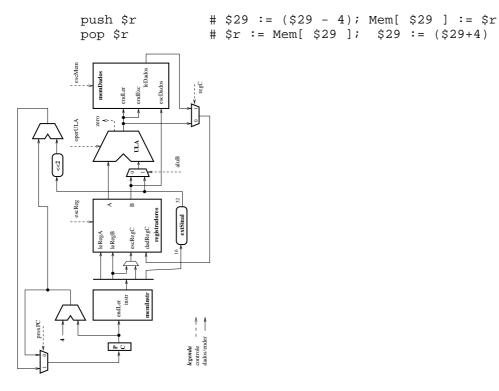

- 3) Mostre as ligações adicionais necessárias para a implementação das instruções PUSH e POP no processador do Capítulo 5, cujo diagrama de blocos está em anexo. Adicione quaisquer recursos que julgar necessários. Mostre os ramos da máquina de estados que implementam estas instruções e indique que sinais são ativos em cada estado. [15 pontos]

# Segunda Prova

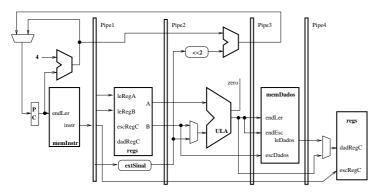

1) Considere o diagrama do processador segmentado abaixo. Existem circuitos de adiantamento de Pipe3 e Pipe4 até as entradas da ULA, e o bloco de registradores é projetado para que valores gravados na entrada fiquem imediatamente disponíveis na saída (escrita transparente).

Para esta seqüência de instruções, responda:

```

add $2, $1, $0

add $3, $2, $1

add $4, $3, $2

add $5, $4, $3

add $6, $5, $4

```

1.1) Quais registradores (dentre \$0..\$31) estão sendo lidos e quais

regs. estão sendo escritos, ao final do quinto ciclo de relógio. [5 pontos]

1.2) Descreva o que a unidade de adiantamento está fazendo ao final do quinto ciclo. [5 pontos]

- 2) Qual é o número total de BITs necessários para implementar uma cache com capacidade para 32Kbytes, palavras de 4 bytes, 8 palavras por bloco, associatividade binária e escrita forçada. Endereços tem 32 bits. Indique as quantidades de bits para cada classe/tipo de informação. [10 pontos]

- 3.1) Faça um projeto detalhado de uma fila de escrita com capacidade para quatro referências pendentes. Considere duas possibilidades para a largura da escrita: (a) uma palavra (<endereço,valor>), e (b) um bloco da cache (<endereço,valor[TAM\_BLOCO]>). [5 pontos]

- 3.2) Qual a relação custo-desempenho das duas implementações, e em qual tipo de cache cada uma das alternativas seria mais adequada? [5 pontos]

#### Terceira Prova

- 1) Usando a notação de Teoria dos Conjuntos, dê expressões que descrevem as relações entre os conteúdos dos registradores (\$0 a \$31), duas caches primárias (dados e instruções), cache secundária unificada, RAM, e área de swapping (suporte a memória virtual). Não esqueça das conseqüências de escritas em todos os níveis. Para as caches, escolha (e INDIQUE) o mecanismo de escrita que mais simplifica as expressões. Considere apenas o processo que está executando no processador e ignore os demais. As expressões devem descrever as circunstâncias nas quais as várias combinações de faltas e acertos podem ocorrer. [15 pontos]

- 2.1) Descreva em detalhe o mecanismo necessário para encontrar uma palavra em uma cache associativa. [5 pontos]

- 2.2) Descreva em detalhe o mecanismo necessário para inserir um novo bloco em uma cache associativa com escrita preguiçosa, com a possibilidade de reposição. [5 pontos]

- 3) Para cada um dos casos abaixo, indique as situações em que seu uso traz vantagens, ou desvantagens, do ponto de vista do desempenho global do sistema. O sistema possui um processador super-escalar e caches. [10pts]

- a) entrada e saída por programa (programmmed I/O);

- b) entrada e saída por interrupções;

- c) entrada e saída por interrupções e DMA (acesso direto à memória).

- 4) Considere um sistema de memória com um barramento com relógio de 200-MHz (5ns). O sistema de memória transfere blocos de 16 palavras, 2 palavras por ciclo de transferência. Na leitura, a seqüência de eventos é:

- 1. 1 ciclo para enviar o endereço para a memória;

- 2. 2 ciclos de latência da DRAM;

- 3. 8 ciclos para transferir 16 palavras.

Na escrita, a sequência de eventos é:

- 1. 1 ciclo para enviar o endereço para a memória;

- 2. 8 ciclos para transmitir 16 palavras;

- 3. 1 ciclo de recuperação.

Calcule a taxa máxima de transferência (bandwidth) em MBytes/segundo para um padrão de acessos com 30% de escritas e 70% de leituras. [5 pontos]

## Exame Final

- 1.a) Enumere e descreva QUATRO causas para exceções no processador segmentado (pipeline) do Capítulo 6. Desenhe um diagrama simplificado do processador e mostre os locais onde as exceções ocorrem e são detectadas. [20 pontos]

- 1.b) Liste a seqüência de eventos associados ao tratamento de uma exceção, considerando todos os efeitos no processador e na hierarquia de memória (com dois níveis de cache e TLB). [20 pontos]

- 2) O trecho de código C abaixo poderia ser usado como parte de um simulador de caches. Os tipos de dados não estão definidos mas o código descreve com precisão as ações que ocorrem durante um acesso de leitura a uma cache com mapeamento direto.

```

static Entry cache[CACHE_SIZE_IN_WORDS];

word ReadDirectMappedCache( address a ) {

Entry e; int i;

e = cache[a.index];

if (e.valid == FALSE || e.tag != a.tag) {

e.valid = TRUE;

e.tag = a.tag;

e.data = load_from_memory(a);

}

return e.data;

}

```

Modifique o código acima de duas maneiras:

- a) para que o código simule oe eventos em uma cache com blocos com quatro palavras de largura; e

- b) para que ele trate também das referências de escrita em uma cache com escrita preguiçosa (write-back).

- A função recebe um parâmetro que indica se a referência é de leitura (wr==FALSE) ou escrita (wr==TRUE). [40 pontos]

- 3) Nas respostas de provas desta disciplina ocorrem com alguma freqüência instruções como lw r, s, t com uma semântica que imagino ser r := Mem[(s+t)].

- 3.a) Mostre uma possível implementação desta instrução no processador não-segmentado visto em aula (diagrama abaixo). [10 pontos]

- 3.b) Discuta a viabilidade de se implementar esta instrução no processador segmentado do capítulo 6. [5 pontos]